Cadence Soc Encounter

Cadence Soc Encounter 81

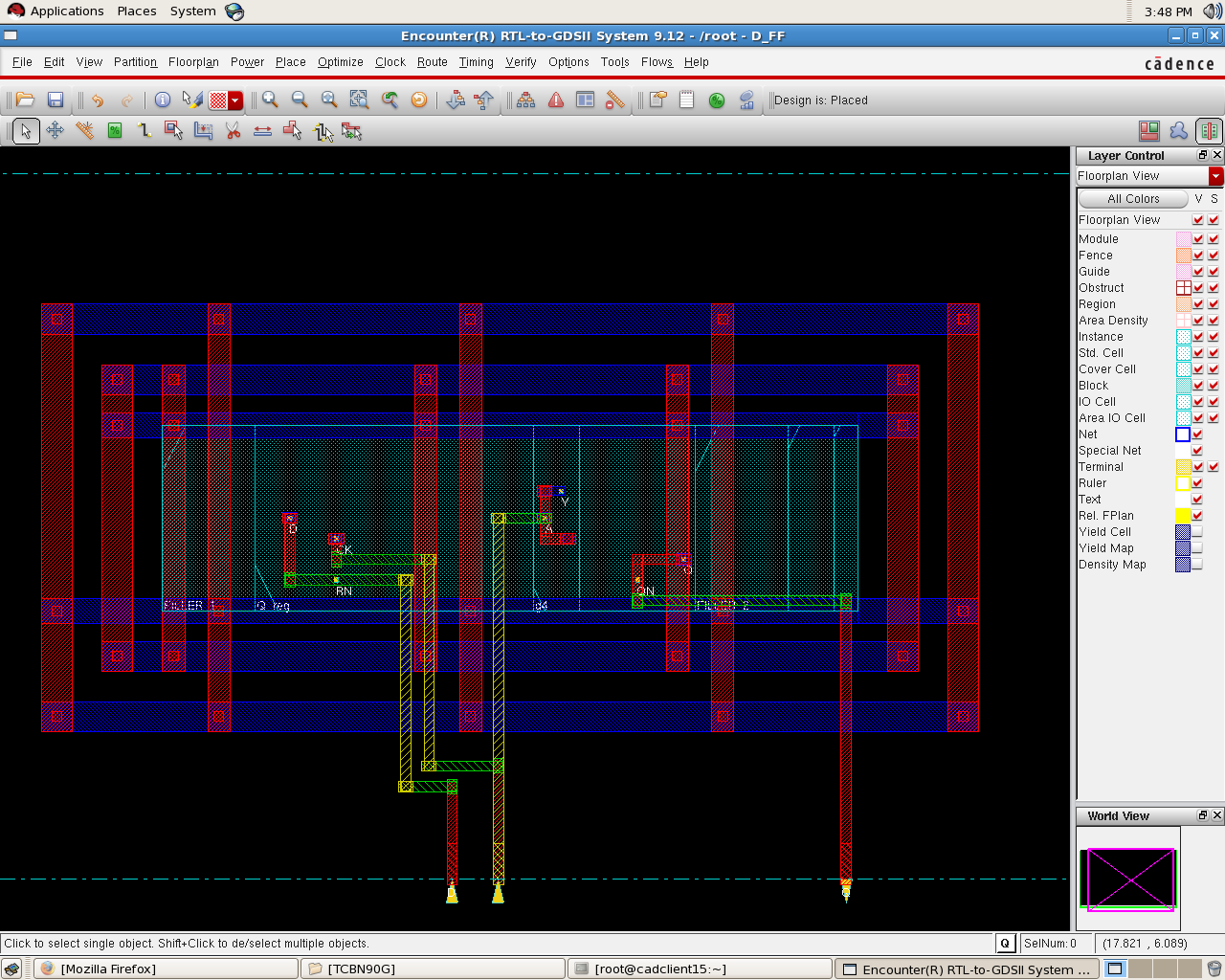

More Cadence Soc Encounter videos. J M Emmert Starting Encounter • To start the tool, first you must source the environment file source set_cadence_soc_env –This file sets up the paths and. Tutorial for Encounter RTL-to-GDSII System 13.15 T. Manikas, SMU, 3/9/15 1 Tutorial for Cadence SOC Encounter Place & Route. For Encounter RTL-to-GDSII System 13.15.

Achieving rapid design convergence in large, complex chips requires greater capacity, accuracy, and automation than what conventionally rigid hierarchical design flows can provide. With Cadence ® hierarchical design and floorplanning technologies, you’ll have fewer iterations and significantly shorter turnaround time. Unified timing and extraction engines across an integrated flow bring predictable design closure and convergence. Innovus Implementation System Optimized for industry-leading embedded processors, as well as for 16nm, 14nm, and 10nm processes, the Innovus implementation system helps you get an earlier design start with a faster ramp-up. With unique new capabilities in placement, optimization, routing, and clocking, the Cadence Innovus ™ Implementation System features an architecture that accounts for upstream and downstream steps and effects in the design flow. This architecture minimizes design iterations and provides the runtime boost you’ll need to get to market faster. Using the Innovus Implementation System, you’ll be equipped to build integrated, differentiated systems with less risk.

First Encounter Design Exploration and Prototyping Enables quick full-chip virtual prototyping to accurately capture downstream physical/electrical impacts at the beginning of the design cycle. Unique partitioning and budgeting capabilities combined with GigaFlex Abstraction Technology make hierarchical implementation easier and faster for giga-scale, high-speed designs.